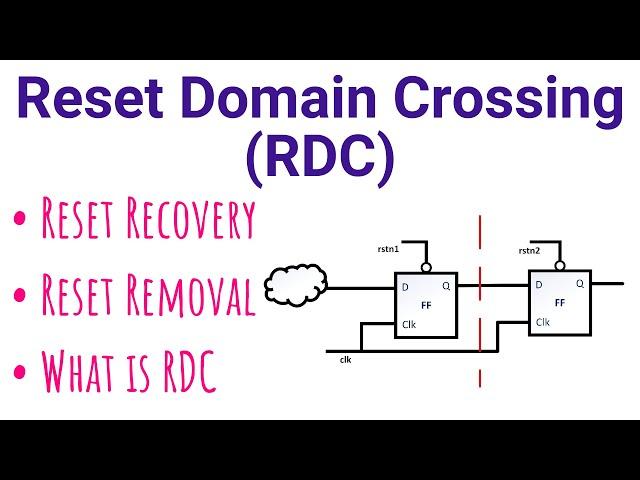

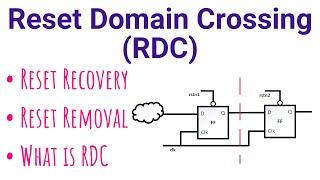

Reset Domain Crossing (RDC) Basics | Reset Recovery | Reset Removal | RDC Basics | VLSI Interview

Комментарии:

RDC Issue is basically source reset to destination clock issue. It is related to reset assertion which means that if reset of source flop gets asserted and it causes input signal to destination flop change during aperture window of destination flop then that flop goes into metastability.

The point here you are making is reset de assertion. Here, What happens is that if reset gets deasserted in the recovery - removal window of the flop, then it will cause metastability, which further means during that window period, reset signal should be stable.

Yes, It can also cause destination flop goes into metastable state but It will be not be treated as RDC issue. This will be another form of CDC only. It can be taken using reset synchronization using reset synchronizers.

not only deassertion! rstn1 could also assert at a point close to clock edge and flop2 can have metastability due do data change to 0 close to edge

Ответить

Hi,

Nice one. I've a question. Which is a best way for a DV engineer to verify the reset tree?

RDC is assertion issue not the de-assertions. and also if you can cover reset ordering as one of the techniques to solve the RDC.

Ответить

RDC is assertion problem and not the deassertion problem, please do correct

Ответить

Hi, can you please draw timing diagrams to indicate what happens when reset is de-asserted during recovery or removal time? That will help in better understanding of concept.

Ответить

![[FREE] Alternative Rock + Indie Pop Type Beat "ecstasy" [FREE] Alternative Rock + Indie Pop Type Beat "ecstasy"](https://rtube.cc/img/upload/RWFDeFBtdkZRdlI.jpg)

![Stargate [SFC, SNES] Stargate [SFC, SNES]](https://rtube.cc/img/upload/d2IzTFZXMGhzOVg.jpg)